# **Minimal Example Demos**

最小限のサンプルデモ

Last updated in RT Box TSP 3.1.2

# 1 はじめに

これらのRT Boxの最小限のサンプルデモは、1台のRT Box上で動作する基本的な電力変換トポロジを特徴としています。 これらのデモモデルには以下の機能があります:

- ・ コンバータトポロジは、該当する場合はPLECSライブラリのNanostepモジュールコンポーネントを使用して、またはPLECS ライブラリのパワー素子モジュールのデフォルトSub-cycle average構成を使用して適用します。

- PWM信号の生成は、コンバータトポロジがリアルタイムで動作するのと同じRT Box上で、単純な開ループパターンを使用して行います。

- モデルを1台のRT Boxにデプロイするには、RT Boxの前面パネルにあるDigital OutインタフェースとDigital Inインタフェースを接続するためのループバックケーブルが必要です。

このドキュメントでは、最小限のサンプルデモの共通概念について説明しています。基本的なコンバータトポロジに対するRT Boxの実行機能を紹介することに重点を置いています。ここでは、実際のコンバータ設計のパラメータを提供することを意図していないことに注意してください。

選択した離散化ステップサイズとCPUの平均実行時間、および各最小限のサンプルデモのFPGAステップサイズを<u>表1</u>に示します。RT BoxのNanostepソルバは、1桁台のナノ秒範囲の時間ステップでコンバータをシミュレートします。NanostepソルバのステップサイズはRT Boxハードウェアに基づいて固定で、RT Box 1およびCEは7.5ナノ秒、RT Box2および3では4ナノ秒です。誘導性ACリンクを備えた高周波DC/DCコンバータを正確にモデル化するには、小さなステップサイズが重要です。

### 1.1 要求仕様

このデモモデルを実行するには、次の製品が必要です(www.plexim.comから入手可能):

- ・ PLECSおよびPLECS Coderライセンス1つづつ(バージョン4.9.1以上)

- 1台のPLECS RT Box CE、1、2または3

- ・ RT Box Target Support Packageバージョン3.1.1以上

- RT Box の初期セットアップについては、RT Box User Manualのクイックスタートガイドに記載されている、PLECSとRT Box の設定手順に従います。

- ・ 37ピンD-Subケーブル1本

注意 このモデルには、以下からアクセスできるモデル初期化コマンドが含まれています:

PLECS Standalone: シミュレーションメニュー -> シミュレーション・パラメータ... -> 初期化

PLECS Blockset: Simulinkモデルウィンドウで右クリック -> モデルプロパティ -> コールバック -> InitFcn\*

# 2 モデル

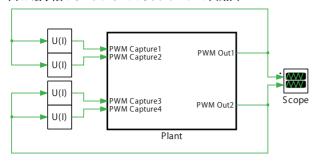

すべての最小限のサンプルデモは同じセルフループバック概念に従っているため、以下ではflying\_cap\_single\_phase\_inverter.plecsモデルを使用して説明します。図1は、モデルのトップレベルの回路図を示しています。

ユーザは、最上位レベルの回路図にPLECSスコープを追加して、生成された理想PWM信号をPC上のオフラインシミュレーションで視覚化できます。

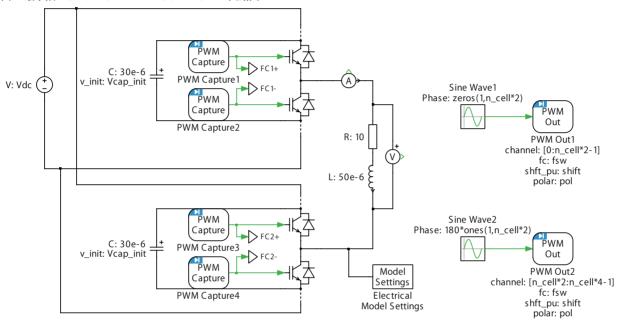

"Plant"サブシステムには、コンバータトポロジとPWM生成ロジックの両方が含まれています。図2は、"Plant"サブシステム内の回路モデルを示しています。

表1: 最小限のサンプルデモの離散化ステップサイズ

| Model Name                               | RT Box 1<br>CPU | RT Box 2 or 3<br>CPU,<br>FlexArray | Nanostep<br>(7.5 ns on RT Box 1,<br>4ns on RT Box 2 or 3) |                            |          |                |     |

|------------------------------------------|-----------------|------------------------------------|-----------------------------------------------------------|----------------------------|----------|----------------|-----|

|                                          |                 |                                    |                                                           | Buck Converter             | 1.25 μ s | 2.0 μs , 250ns | Yes |

|                                          |                 |                                    |                                                           | Synchronous Buck Converter | 1.25 μ s | 2.0 μs , 250ns | Yes |

| Boost Converter                          | 1.25 μ s        | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Flyback converter                        | 1.5 μ s         | 1.5 μ s , 250ns                    | Yes                                                       |                            |          |                |     |

| Single-Phase Inverter                    | 1.5 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Three-Phase Inverter                     | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Three-Level NPC Inverter                 | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Three-Level NPC Inverter                 | 5.0 μ s         | 2.0 μs , 500ns                     | N/A                                                       |                            |          |                |     |

| (two interleaved branches with breakers) |                 |                                    |                                                           |                            |          |                |     |

| Three-Level T-Type Inverter              | 2.5 μ s         | 2.5 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Three-Level ANPC Inverter                | 2.5 μ s         | 2.5 μs , 417ns                     | N/A                                                       |                            |          |                |     |

| Vienna Rectifier                         | 2.5 μ s         | 2.5 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Five-Phase Inverter                      | 5.0 μ s         | 2.5 μs , 417ns                     | N/A                                                       |                            |          |                |     |

| Five-Phase Interleaved Sync. Buck        | 3.5 μ s         | 2.5 μs , 417ns                     | N/A                                                       |                            |          |                |     |

| Flying-Cap Single-Phase Inverter         | 6.0 μ s         | 4.5 μs , 450ns                     | N/A                                                       |                            |          |                |     |

| Cascaded Full-Bridge Rectifier           | 6.0 μ s         | 4.5 μs, 900ns                      | N/A                                                       |                            |          |                |     |

| Dual-Active Bridge                       | 1.8 μ s         | 1.8 μs , 257ns                     | Yes                                                       |                            |          |                |     |

| Half-Bridge LLC                          | 1.8 μ s         | 1.8 μ s , 257ns                    | Yes                                                       |                            |          |                |     |

| Full-Bridge LLC                          | 1.8 μ s         | 1.8 μs , 257ns                     | Yes                                                       |                            |          |                |     |

| Phase-Shifted Full-Bridge                | 1.8 μ s         | 1.8 μs , 257ns                     | Yes                                                       |                            |          |                |     |

| CLLLC                                    | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| NPC CLLLC                                | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Three-Phase Dual Active Bridge           | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

| Triple Active Bridge                     | 2.0 μ s         | 2.0 μs , 250ns                     | Yes                                                       |                            |          |                |     |

## 2.1 コンバータトポロジ

該当する場合、コンバータのスイッチングレッグは、PLECSライブラリのNanostepセクションで利用可能なモジュールを使用して構築します。RT BoxのNanostepソルバは、1桁台のナノ秒範囲の時間ステップでコンバータをシミュレートします。トポロジにNanostep実装がない場合、PLECSライブラリのパワー素子モジュールを使用してデフォルトのSub-cycle average構成でモデル化します。

パワー素子モジュール内の**アサーション**はすべてデフォルトでオンに設定されています。リアルタイム実行中に、補完スイッチペアのゲート信号の重複を捕捉できます。RT Boxはエラーメッセージを表示します。

電気モデル設定ブロックはコンバータのブリッジレッグに接続しています。このブロック内では、**ターゲット**としてCPUまたは FPGAを選択します。

#### 図1: 最小限のサンプルデモのトップレベルの回路図

図2: 最小限のサンプルデモのPlantサブシステムの回路図

- ・ CPU すべてのRT Boxで使用可能で、RT Box 1にビルドする場合のデフォルトのオプションです。

- FPGA RT Box 2および3でのみ使用可能で、RT Box 2または3上にビルドする場合のデフォルトのオプションです。

また、離散化ステップ サイズTs\_plantは、異なるシミュレーションターゲット間で微調整される場合があります。詳細については、各デモのモデル初期化コマンドを参照してください。

## 2.2 PWM生成とキャプチャ

RT Box Target SupportライブラリのPWM Outブロックは、PWM信号を生成するために使用します。Carrier phase shift、Carrier limits、Polarityなどのパラメータは、RT Box上でさまざまなトポロジのゲート信号パターンを生成するために使用します。

RT Box Target SupportライブラリのPWM Captureブロックは、ループバック方式で自己生成したPWM信号をサンプリング するために使用します。FPGAシミュレーションの場合、前提条件として、PWM Captureブロックをパワー素子モジュールの ゲートに直接接続する必要があることに注意してください。 - これは、すべての最小限のサンプルデモの実装に適用しています。 パワー素子モジュールがNanostep用に設定されている場合、PWM信号はRT Box 1およびCEでは7.5ナノ秒間隔でサンプリング し、RT Box 2および3では4ナノ秒間隔でサンプリングします。これはNanostepソルバの実行間隔です。

# 3 シミュレーション

最小限のサンプルモデルを1台のRT Boxにデプロイするには、以下の手順に従ってください:

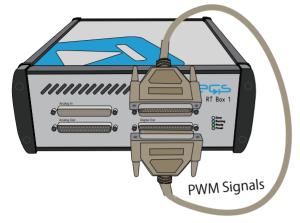

図3: 最小限のサンプルデモを実行するために前面にループバックケーブルを接続したRT Box

- 1 図3のようにDB37ケーブルを使用して、RT BoxのDigital OutインタフェースをDigital Inインタフェースに接続します。

- 2 Coderオプション ウィンドウのシステムリストから、"Plant"を選択し、ユーザのRT Boxにビルドします。

- 3 モデルがアップロードされたら、**Coder オプション...**ウィンドウの**外部モード**タブから、RT Boxに接続し、**自動トリガを有効化** にします。

- 4 ユーザは、"Plant"サブシステム回路図内に接続されているPLECSスコープからリアルタイムの波形を表示できます。

- **5** ユーザは、RT Box Web Interfaceの**Application**タブと**Diagnostics**タブで、CPUまたはFPGAシミュレーションのリアルタイムパフォーマンスに関する詳細情報を見ることもできます。

# 4 まとめ

これらの最小限のサンプルデモでは、1台のRT BoxでPWM信号ループバックを設定する簡単な使用方法を紹介しました。 CPUまたはFPGAシミュレーションは、電気モデル設定ブロックを使用してPLECSモデルで設定できます。 改訂履歴:

RT Box TSP 3.0.1 初版

RT Box TSP 3.0.3 2つのインタリーブブランチを備えたNPCインバータデモを追加

RT Box TSP 3.1.2 デモをNanostepソルバに更新し、さまざまな新トポロジを追加

plexim

Pleximへの連絡方法:

☎+41 44 533 51 00 Phone

+41 44 533 51 01 Fax

⊠ Plexim GmbH Mail

Technoparkstrasse 1

8005 Zurich

Switzerland

@ info@plexim.com Email

http://www.plexim.com Web

# AUTO AD\ANATION アドバンオートメーションへの連絡方法:

**☎** +81 3 5282 7047 Phone

+81 3 6285 0250 Fax

⊠ ADVAN AUTOMATION CO.,LTD Mail

1-9-5 Uchikanda, Chiyoda-ku

Tokyo, 101-0047

Japan

@ info-advan@adv-auto.co.jp Email

https://adv-auto.co.jp/ Web

#### RT Box Demo Model

#### © 2002–2025 by Plexim GmbH

このマニュアルで記載されているソフトウェアPLECSは、ライセンス契約に基づいて提供されています。ソフトウェアは、ライセンス 契約の条件の下でのみ使用またはコピーできます。Plexim GmbHの事前の書面による同意なしに、このマニュアルのいかなる 部分も、いかなる形式でもコピーまたは複製することはできません。

PLECSはPlexim GmbHの登録商標です。MATLAB、Simulink、およびSimulink Coderは、The MathWorks、Inc.の登録商標です。その他の製品名またはブランド名は、それぞれの所有者の商標または登録商標です。